PUP: a host of Perfectly Usable Phasers

- Oct 22, 2022

- 15 min read

Updated: May 13, 2023

I’ve always liked phasers, in fact one of my first pedals I’ve ever built was a Phase 45 clone. Not only I liked how it sounded, another main reason for choosing it (other than the complexity) was that I only needed two matched JFETs instead of, for example, four for a four-stage phaser.

I’ve been sitting there, content with my box, for some years, until recently I’ve heard of the Project 447 phaser on an old ETI magazine. It wasn’t perfect by most accounts (the long string of 741 op-amps in series with the signal probably didn’t help noise-wise), but it exploited a CD4049 unbuffered hex inverter as the source of Voltage Controlled Resistors, with the idea behind it that FETs on the same die will be practically matched by nature. Specifically, the ETI phaser uses the NMOS devices: the PMOS are in parallel, since the supply rails are shorted, but they won’t conduct since the gates are biased up from the source voltage.

This amazed me. Not only I hadn’t thought before of using the MOSFETs inside a CMOS inverter this way, but I was happy to find a working example of MOS as VCR in a phaser, something I had contemplated before, since their use as cheaper VCR than JFETs is not unheard of, especially in synth projects, but which I had some doubts about because of the presence of the body diode which strongly harms linearity with anything other than small signals.

Before I knew it, I discovered even more phasers using the same principle, one being the Jen KPS-900 and another being the EHX Bad Stone, a circuit unjustly shadowed by the similar-named Small Stone, but with a beautiful schematic I suggest analyzing, once you can bring some order into it. The former uses the PMOS in the CD4007, the latter the NMOS in the oddball inverter CD4009, but the principle is the same.

Next, I even found a nice series of articles on EDN about FET VCRs, analyzing and demonstrating JFET and MOSFET equally in different applications, including a phaser effect (there’s 5 parts to the series, make sure to use the search function to find them all!).

This is to say that, while the idea isn't certainly new, it's surely a bit neglected, and I hope that in doing this I'm sharing a way for the DIY enthusiast to make cheap and easy to build phasers or other effects requiring multiple VCRs: this was a long journey made up of uncharted territories and violated assumptions, but it brought its results in the end.

The basic principle

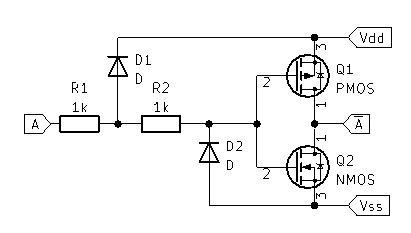

The above pictures show the internal schematic of a 4069 section, as shown in the datasheets, and what it turns into when wired as in the following circuits: leaving Vdd disconnected excludes both the PMOS and a protection diode, while the other is welcome to stay. The bulk terminals are connected the same as shown in the datasheet. The inverter inputs are the gate terminals, the output is the drain connection, Vss the common connection to all sources when using the NMOS.

Resistance measurements

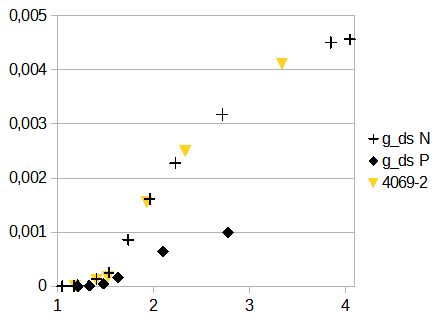

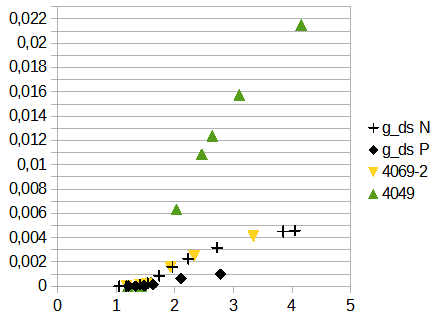

To start laying down the ground for my CMOS phaser, I first measured the Rds channel resistance against Vds. The setup was so simple there’s no need for a schematic: I connected a potentiometer divider to the gate (any of the inputs), referenced the source to the appropriate supply rail (connecting Vss to - to measure the NMOS, Vdd to + to measure the PMOS) and measured the resistance between drain (the output of each section is connected to both the drains of the pair) and source. This was mostly to get a rough idea of the resistances and gate voltages I was working with. I’ve done this test with one of the NMOS and PMOS of my first 4069 chip, then compared it with the NMOS of a different 4069 and with the NMOS of a 4049.

I've plotted the conductance including and excluding the 4049, both to show better the 4069 and the differences between the two.

We can see that in general we can have resistances from infinite to few hundred ohms with Vgs from 0 to 4V or more and that the conductance is close to linear over a useful range.

The 4069 PMOS is weaker than the NMOS, not being able to go below 1kΩ in these conditions, while the NMOS in the 4049 is even stronger, readily going below 100 ohms with lower gate voltage. This agrees with the common knowledge. I was leaning into using the 4069 already, given I had more of them, but I was glad that the choice was supported by the measurements, giving me control over a useful range of resistances with a less narrow Vgs range. I don’t doubt the following circuits will work with a 4049, but it will require at least an adjustment of the LFO amplitude to compensate for the difference.

Distortion measurements

Next, I’ve set up a circuit to measure the harmonic distortion. This was nothing else that a 250mV RMS 1kHz sine into a voltage controlled attenuator with a 10k resistor in series with the signal and the NMOS shunting the signal to ground with another 10k resistor in parallel, all this AC coupled. I varied the gate voltage with a pot as before. What I noticed was that distortion in all cases peaked just before the FET started attenuating the signal, which corresponds to when it’s barely conducting and has the largest signal across it, then went down to 1% or so with more attenuation. This seems in agreement with what's written in this app note. This was the case both with and without negative feedback to the gate. I thought biasing the drain a bit positive would help avoid issues with the body diode, but in fact it made things worse in this regard, maybe because keeping Vds low is the important thing here. Still, I was not discouraged by these results, both because the distortion was high only in a short range of Vgs and because my intended application was different from this. I’m glad I kept going because the results have been better than I had expected from these premises, I’d say more than Perfectly Usable, nice indeed!

2-stage PUP

Having gathered this data, I went on to make the simpler CMOS PUP, a two-stage one roughly similar to a Phase 45, with the intention of building upon this if all went to plan. This one is a serious contender for the simplest, cheapest Perfectly Usable Phaser you can build, since it’s both compact and without the need of matched components.

I will explain here the sections of the circuit, most of which will figure again in the others:

The input buffer and output unity-gain summing amplifier don’t need many explanations: high impedance input, low impedance output (70s phasers had an unhealthy passion for passive summing, leave alone what’s going on with the amplifier at the output of the phase 90);

The “phase shift” path is made of the usual all-pass filter stages, with the variable resistor to ground instead of in series with the signal. The resistors in the inverting path are largely irrelevant as long as they’re the same, so as usual in these cases I defaulted to 10k, a nice compromise between loading the op-amp and adding Johnson noise (I guess I have an unhealthy passion for that value). The capacitor and fixed resistor aren’t critical either, just keep in mind that the combination of capacitor and resistor determines the lowest frequency of the sweep (the parallel FET is negligible), the capacitor and the minimum resistance of the FET determine the highest frequency (this is also affected by LFO amplitude and bias to a point). The resistor also has the functions of biasing the non-inverting input and making sure the drain voltage, hence the Vds, stays there too. Too large of a value will result in audible distortion, probably because of the larger variations in Vds.

The LFO is the two-opamp schmitt trigger plus integrator triangle oscillator. This more-or-less textbook form gives a low impedance triangle wave with linear ramps and is similar to the one in the Boss CE-2 and many others. Another nice thing about it is that it allows good control of the rate with a logarithmic or linear pot, just by attenuating the schmitt trigger output. Unlike in the Boss version, this attenuator doesn’t go to the voltage reference, which caused audible ticking even with generous decoupling, but to a dedicated divider, which also doubles as stopper resistor setting the lowest frequency (the 5k parallel combination of the two).

The LFO is summed together with the gate bias voltage with two resistors. The bias voltage comes from a trim pot and is made to be at least equal to the source voltage (Vr). This resistor network also attenuates the LFO by the right amount, and the two are inseparable with DC coupling, even if I saw some phasers using a depth control with DC coupling. This brings me to what I call “leverage”. Why didn’t I make the LFO smaller to begin with, so I have to attenuate it less? By the nature of the schmitt trigger, it works with the op-amp saturation voltages, so it’s roughly centered between the supply rails. Attempting to bias it far from it just breaks it, so its output will be centered around 4.5V. You can think of this as a voltage divider between bias and 4.5V, determined by R11 and the bias source resistance: if I attenuated the LFO less, even turning the bias trim up to 9V wouldn’t result in a high enough bias voltage. That’s why I settled on those values, which gave me the right amount of modulation and allowed me to bias without bottoming out the trim pot. Actually, I’ve then discovered that the JH 20-pole phaser uses a clever trick with a diode in the schmitt trigger feedback loop that shifts the lfo in the positive or negative half of the supply, but for how cool this is, I didn’t feel like it was necessary as long as I had enough “leverage” to bias effectively. C4 deserves a few words: it has the double function of attenuating the LFO at high rates, which otherwise results in a “seasick” effect, and keeping this node at low impedance for audio frequencies for the feedback explained below.

The resulting gate voltage goes through a feedback divider for each of the FETs. This has the purpose of reducing distortion caused by drain voltage variations by nothing other than the signal. This is sometimes present in JFET phasers, sometimes not, but it definitely necessary for MOSFETs. As detailed in the EDN articles, half of the signal has to be fed to the gate for maximum cancellation. The resistors are made large compared to both the drain and the LFO+bias impedances. The only downside of doing this is that the resulting gate drive is half of what’s coming before the resistors, so this means the LFO and bias both need to be larger to compensate. This is achieved with the shown values.

The Vss pin of the 4069 is connected to the voltage reference. This connects to all the NMOS sources, which are all in parallel: not an issue for this application. I didn’t need to connect Vdd, and so the PMOS sources, to anything, since they’re not used and they’re harmless this way.

While this is a fine-sounding circuit and a compact one too, those four unused inverters are staring at me from the side, so let’s do something about that. A 4007 might be a good alternative for the PUP 2, although it’s not any smaller. Here's what it sounds like:

4-stage PUP

While personally I enjoy the subtler 2-stage phasers, I know many prefer 4-stage ones, so this one is for you and it’s where things get interesting. This one is reminiscent of the Phase 90.

Most of the circuit is unchanged, save for a few tweaked values. The resistors in parallel to the FETs are now 10k, which makes the effect not sweep as low in frequency. I enjoy this more “swirly” sound as opposed to the “bubbling” one of a larger resistor like 15k, but they’re both valid and something I encourage to try.

Since there are four stages now, we can have feedback! There are many possibilities, from any of the outputs to any of the inverting inputs, although some of them aren’t useful. Of the remaining ones, the one shown was my favorite. A 22k resistor was a nice compromise between being audibly different from no feedback and too much feedback that the circuit stops working, but you can try different values. You might think a potentiometer here would allow for variable amounts of feedback, but the inverting inputs are not at virtual ground! This means that as long as the feeedback is connected, even a large resistor or a divider that sends the resistor to Vr will affect the phaser response negatively, unless you want to have both the switch and the pot, which seems unnecessary to me.

Trimless 4-stage

There are still two unused inverters sitting there. While the logical continuation is making a 6-stage phaser, chronologically the last challenge I wanted to try has been using one of them to set the bias of the others without manual trimming, still keeping in mind that they’re all matched. These circuits aren’t meant for mass production, so turning a trimmer isn’t so bad, but I liked the elegance of a phaser working without having to touch it, and the Bad Stone achieved this in its own way, so I wanted to find a way even if it required more time and effort than it was worth it for me.

The signal path is unchanged, this is still the same phaser. What changes is the control circuit. The LFO is switched to a single-opamp one, since the other section is used for the bias servo. In this final arrangement, the two are mixed together in the same way as before, but with the LFO AC coupled so that it doesn’t change the DC bias coming from the servo.

The principle of the servo is simple to explain and similar to the one in the EDN articles. The op-amp tries to make the voltage on both inputs equal: since the FET is equivalent to a common source amplifier, the non-inverting input results in negative feedback. I had calculated as first guess a resistance value to center the modulation on of 2.2kΩ, which is 2.8kΩ in parallel with the 10kΩ fixed resistor. If you imagine R25 and the FET as a voltage divider, this means, since R12 is 10 times bigger, that R13 has to be 28kΩ.

In practice, I used a value of 33k because there are some sources of error. One of them is the op-amp offset voltage. The drain and divider voltages are some tens of mV above Vr, so even 1mV might throw things off considerably. The other is that even if R25 is large and there’s the same negative feedback as in the FETs in the phaser itself, its conditions aren’t quite the same. As it is, the Vds of the servo MOSFET has been measured at 19mV. I had to balance these two effects: if I used a larger value for R25 to reduce Vds, this either meant a Vds comparable to the offset voltage or scaling up the R12/R13 divider further, but 10M is at the upper limit of commonly used values. You could use a low offset, low bias current op-amp, but the results will probably need to be tweaked anyway, and R18 is another source of error, being in series with the linearizing 10M resistors, even if I made those larger to reduce the effect.

What matters is that I’ve compensated for those effects already, and you should get a phaser that behaves as intended with any 4069 (or possibly 4049, but remember to adjust the LFO) you plug in.

I’ve lowered the voltage reference to 3.6V because U2D has to output a voltage which is about 3V above that, since the gate drive gets halved by the feedback too. A 4.5V Vr worked, but the op-amp output was too close for comfort to the positive saturation voltage, given also that mine is just one sample of 4069. The MOSFET linearity will probably give issues before this becomes one anyway.

Since this is its first appearance here, it’s worth spending a few words about the single op-amp LFO. The trade-offs is that now the rate control should be C taper, the triangle wave is made from exponential ramps, and the output isn’t nicely buffered so I had to put some care into not loading the output down and making it asymmetrical. Other than this, it’s functionally equivalent and tied with the two op-amp one for the most popular triangle LFO around.

I’ve tweaked the amplitude and rate to my needs. A smaller amplitude results in a more linear triangle wave, but this wasn’t a choice because of the aforementioned “leverage” and the limit on the smallest resistor I could use on the output (increasing R18 increases the bias servo error if you recall). This is also why I suggested a combination of a 50kΩ pot with a 22uF capacitor, instead of the more common and mostly equivalent 100kΩ and 10u. The former combination has lower impedance and can be loaded down further before you start to see the effects, and this seemed a valid trade-off, since you can also just use a 100kΩ pot with the 22uF capacitor: it will just go slower when set at minimum.

One note about capacitor C2: the triangle signal is fed back into the schmitt trigger with a 1M resistor, which isn’t a significant load on it; this capacitor acts somewhat like an integrator and has the very welcome effect of smoothing the sharp transitions of the schmitt trigger output and in the triangle wave itself, reducing the chances of popping. The side effect is that the LFO amplitude increases slightly at higher rates if this capacitor is made too large, but that can easily be countered by C8.

Here's what it sounds like (trim version):

6-stage PUP

This is the natural endpoint for these CMOS phasers: having access to six matched devices allows for six variable all-pass filters, which would otherwise lead to the grueling task of getting six matched JFETs or resorting to LDRs or OTAs.

Some parts of the circuit are familiar, but others have changed:

The output mixer is still unity gain for the dry signal, but has a gain of 3.3 for the “phase shifted” signal. This is to compensate for the attenuation introduced by U1B. In the end though, the signals still get mixed and cancel as before. The “polarity” switch allows to have the dry signal in phase (2→3) with the “phase shift”, for a classic phaser, out of phase (2→1) for a phaser that swaps the notches for peaks with notches in between, or no dry signal for a vibrato effect. The “6-4” switch takes the output after 6 or four stages.

U1B’s main purpose is to attenuate the signal going into the all-pass filters a precise amount while keeping it low impedance. This was necessary because the distortion introduced by having six FETs was audible on the louder signals. This small amount of attenuation is enough to fix the problem completely also for consumer line levels. Since I had to accept this small loss in terms of one extra stage and the noise from the attenuation (small as it is in dB), I made the best I could out of this stage and used it as input for the feedback signal, in a manner similar to the MuTron Phase II. This time, we can also have a pot to control the feedback, down to zero, without the output being affected with this still in the circuit but at zero!

The all-pass filters are pretty much the same, with the same notice that the fixed 10kΩ are according to my personal taste.

The LFO is the single op-amp one described above, with few value changes regarding the loading, attenuation and C14.

The linearizing resistors have been scaled up, because once you have this many, you start noticing that they’re acting as a resistor of a value of a third of a single one of them (6 series pairs in parallel) dragging the LFO node down to Vr and not allowing to bias as intended. Scaling up to 2.2M solved this issue.

Feedback is where it gets fun: going from four to six stages, there are suddenly many more viable options (but still some duds), so many in fact that the ones I went for are only a curated selection within the limits of a two-position “feedback” switch and a two-position center-off DPDT “polarity” switch, of which I used the second pole here to change feedback options depending on the phaser polarity. This allowed me to get my two favorite settings for each mode, but means there’s no feedback in vibrato mode. I consider this a fair trade-off since this mode is more of a free extra than anything. One can always go crazy and have something like a 6-position rotary switch to get access to all the options, viable or not, at all times, or an on-on-on DPDT switch wired as SP3T, but for me this is a more than wide enough selection of weird sounds. The “feedback” pot is linear with R5 and R1 not tapering it to logarithmic: this is intentional because feedback is very subtle in low amounts, so this gives better control over the useful range. The maximum amount is chosen to be high but safe at all settings by these two resistors, but you’re free to increase it further at your own risk. C1 is a trick I got from MuTron: without it limiting the feedback at high frequencies, it was almost guaranteed to have oscillation, either audible or ruining the sound completely.

Here's how it sounds like in a demonstration of all modes featuring both guitar and E-piano:

Since I've recorded them, here's all the usable feedbacks for both polarities:

Bonus: single FET phaser

Did I say the 2-stage PUP was a contender for easiest to build phaser around? This one might beat that in terms of sheer simplicity. While I was working on the other circuits, I wanted to try as an experiment how much I could get from using a single variable stage and a fixed one. Phasers with fixed stages are pretty common after all, and you still have one frequency at which there’s phase cancellation for every two stages.

Turns out that it works in practice! Since only one stage is variable, to get a good sweep out of it I had to increase the parallel resistor, so that the effective value can vary over a wider range. Sadly, the necessary values are too large for a MOSFET, so no 2N7000 phaser (it’s still a valid idea if you want to match two of them and build a classical 2-stage though): I had to use a JFET, but I think an LDR would work just as well if not better, since it has better linearity than any FET even with the large parallel resistor.

Here's how it sounds like:

The build

I've decided to permanently build the 6-stage phaser for myself. Here are some pictures and a perfboard layout that, even if not the prettiest, fits comfortably in a 125B.

Thanks as usual to aotmr for the continued feedback and support that made this possible.

Be sure to check the thread on FSB for the discussion and layouts!

Great work, Dylan!